# 申威 421 处理器 软件接口手册

2017年10月

成都申威科技有限责任公司

#### 免责声明

本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

#### 成都申威科技有限责任公司

Chengdu Sunway Technology Corporation Limited 地址:成都市华府大道四段电子科大科技园 D22 栋 Building D22, National University Science and technology park, Section 4, Huafu Avenue, Chengdu

Mail: sales@swcpu.cn Tel: 028-68769016 Fax: 028-68769019

#### 阅读指南

《申威 421 处理器软件接口手册》主要描述了申威 421 处理器核心结构、特权指令及程序、内部寄存器 CSR 说明、存储管理、异常终端介绍、初始化复位说明等内容。并详细说明了调试支持和编程优化等内容。

### 文档修订

|            | 文档名  | 申威 421 处理器软件接口手册 |

|------------|------|------------------|

| サ松田がつヨ     | 版本号  | V1.0             |

| 文档更新记录<br> | 创建人  | 研发部              |

|            | 创建日期 | 2017-10-8        |

### 版本更新

| 版本号  | 更新内容 | 更新日期      |

|------|------|-----------|

| V1.0 | 初稿   | 2017-10-8 |

|      |      |           |

|      |      |           |

|      |      |           |

### 技术支持

可通过邮箱或问题反馈网站向我司提交产品使用的问题,并获取技术支持。

售后服务邮箱:sales@swcpu.cn

问题反馈网址: http://www.swcpu.cn/

# 目 录

|   | 1 核心结构概述                                                                                                                                                                                                                                       |                                                                                        |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 2 | 2 处理器模式与特权程序                                                                                                                                                                                                                                   |                                                                                        |

|   | 2.1 处理器模式                                                                                                                                                                                                                                      |                                                                                        |

|   | 2.2 特权程序                                                                                                                                                                                                                                       |                                                                                        |

|   | 2.3 特权指令                                                                                                                                                                                                                                       | 6                                                                                      |

|   | 2.4 系统寄存器                                                                                                                                                                                                                                      | (                                                                                      |

| 3 | 3 控制与状态寄存器                                                                                                                                                                                                                                     |                                                                                        |

|   | 3.1 CSR 的编址                                                                                                                                                                                                                                    |                                                                                        |

|   | 3.2 CSR 访问机制                                                                                                                                                                                                                                   | 10                                                                                     |

|   | 3.3 指令部件中的 CSR                                                                                                                                                                                                                                 |                                                                                        |

|   | 3.4 数据 Cache 管理部件中的 CSR                                                                                                                                                                                                                        | 2                                                                                      |

|   | 3.5 二级 Cache 管理部件中的 CSR                                                                                                                                                                                                                        |                                                                                        |

|   | 3.6 整数部件中的 CSR                                                                                                                                                                                                                                 |                                                                                        |

|   | 3.7 浮点运算部件中的 FPCR                                                                                                                                                                                                                              |                                                                                        |

| 4 | 4 存储管理和存储结构                                                                                                                                                                                                                                    |                                                                                        |

|   | 4.1 存储空间                                                                                                                                                                                                                                       |                                                                                        |

|   | 4.2 Cache 结构                                                                                                                                                                                                                                   |                                                                                        |

|   | 4.3 地址转换缓冲                                                                                                                                                                                                                                     |                                                                                        |

|   | 4.4 存储空间访问方式                                                                                                                                                                                                                                   |                                                                                        |

|   | 4.5 错误检测及错误处理                                                                                                                                                                                                                                  |                                                                                        |

| 5 | 5 中断                                                                                                                                                                                                                                           |                                                                                        |

|   | 5.1 中断源                                                                                                                                                                                                                                        |                                                                                        |

|   | 5.2 中断的优先级                                                                                                                                                                                                                                     |                                                                                        |

|   | 5.3 中断的嵌套                                                                                                                                                                                                                                      |                                                                                        |

|   |                                                                                                                                                                                                                                                |                                                                                        |

| 6 | 6 异常                                                                                                                                                                                                                                           | 80                                                                                     |

| 6 | <b>6 异常</b><br>6.1 DTB 脱靶                                                                                                                                                                                                                      |                                                                                        |

| 6 | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80                                                                                     |

| 6 | 6.1 DTB 脱靶<br>6.2 ITB 脱靶                                                                                                                                                                                                                       |                                                                                        |

| 6 | 6.1 DTB 脱靶                                                                                                                                                                                                                                     |                                                                                        |

| 6 | 6.1 DTB 脱靶<br>6.2 ITB 脱靶<br>6.3 浮点屏蔽故障<br>6.4 不对界故障                                                                                                                                                                                            |                                                                                        |

| 6 | 6.1 DTB 脱靶<br>6.2 ITB 脱靶<br>6.3 浮点屏蔽故障<br>6.4 不对界故障<br>6.5 数据流故障                                                                                                                                                                               |                                                                                        |

| 6 | 6.1 DTB 脱靶<br>6.2 ITB 脱靶<br>6.3 浮点屏蔽故障<br>6.4 不对界故障<br>6.5 数据流故障<br>6.6 指令流故障                                                                                                                                                                  |                                                                                        |

| 6 | 6.1 DTB 脱靶         6.2 ITB 脱靶         6.3 浮点屏蔽故障         6.4 不对界故障         6.5 数据流故障         6.6 指令流故障         6.7 操作码非法                                                                                                                       | 80<br>80<br>81<br>82<br>82<br>82                                                       |

|   | 6.1 DTB 脱靶         6.2 ITB 脱靶         6.3 浮点屏蔽故障         6.4 不对界故障         6.5 数据流故障         6.6 指令流故障         6.7 操作码非法         6.8 算术自陷                                                                                                      |                                                                                        |

|   | 6.1 DTB 脱靶         6.2 ITB 脱靶         6.3 浮点屏蔽故障         6.4 不对界故障         6.5 数据流故障         6.6 指令流故障         6.7 操作码非法                                                                                                                       |                                                                                        |

|   | 6.1 DTB 脱靶                                                                                                                                                                                                                                     |                                                                                        |

|   | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80<br>80<br>81<br>82<br>82<br>82<br>83<br>87<br>87                                     |

|   | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80<br>80<br>81<br>82<br>82<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>88             |

|   | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80<br>80<br>81<br>82<br>82<br>83<br>83<br>83<br>84<br>85<br>85<br>86<br>87<br>88       |

| 7 | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80<br>80<br>81<br>82<br>82<br>82<br>83<br>84<br>85<br>85<br>86<br>87<br>87<br>88<br>88 |

| 7 | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80 80 80 81 81 82 82 82 83 83 86 87 87 89 89 89 89 89 89                               |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算术自陷 7 复位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR                                                                     | 80 80 80 81 81 82 82 82 83 83 83 84 85 86 87 87 88 88 88 88 88                         |

| 7 | 6.1 DTB 脱靶                                                                                                                                                                                                                                     | 80 80 80 80 81 81 82 82 82 83 83 83 84 84 85 86 86 87 87 87 87 87 88 88 88 88 88 88 88 |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算术自陷 7 复位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR 8.2 事件计数的模式 8.3 事件计数的流程                                             | 80 80 80 80 81 81 82 82 82 83 85 86 87 87 89 89 90 92                                  |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算术自陷 7 复位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR 8.2 事件计数的模式 8.3 事件计数的流程                                             | 80 80 80 81 81 82 82 82 82 83 83 85 87 87 89 89 90 90 92                               |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算术自陷 7 复位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR 8.2 事件计数的模式 8.3 事件计数的模式 8.3 事件计数的流程 9 功耗管理 9.1 核心深睡眠                | 80 80 80 80 81 81 82 82 82 83 83 85 87 87 87 88 88 88 88 88 89 90 92                   |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算术自陷 7 复位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR 8.2 事件计数的模式 8.3 事件计数的模式 8.3 事件计数的模式 9.1 核心深睡眠 9.1 核心深睡眠                      | 80 80 80 80 81 81 82 82 82 83 83 84 85 86 87 87 87 87 87 87 87 87 87 87 87 87 87       |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算作码非法 6.8 算位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR 8.2 事件计数的模式 8.3 事件计数的流程 9 功耗管理 9.1 核心深睡眠 9.2 核心浅睡眠 9.2 核心浅睡眠 9.3 关闭浮点部件时钟 | 80 80 80 81 81 82 82 82 83 84 85 87 87 87 89 89 90 90 90 90 90 90 90 90 90 90 90 90 90 |

| 7 | 6.1 DTB 脱靶 6.2 ITB 脱靶 6.3 浮点屏蔽故障 6.4 不对界故障 6.5 数据流故障 6.6 指令流故障 6.7 操作码非法 6.8 算术自陷 7 复位和初始化 7.1 复位的种类 7.2 上电复位 7.3 冷复位 7.4 睡眠复位 7.5 复位后的 CSR 8 事件计数 8.1 事件计数相关 CSR 8.2 事件计数的模式 8.3 事件计数的模式 8.3 事件计数的模式 9.1 核心深睡眠 9.1 核心深睡眠                      | 80 80 80 81 81 82 82 82 83 85 87 87 87 89 90 90 90 90 90 90 90 90 90 90 90 90 90       |

#### 申威 421 处理器软件接口手册

| 10.1 指令流调试支持             | 99  |

|--------------------------|-----|

| 10.2 数据流调试支持             | 100 |

| 11 编程优化                  |     |

| 11.1 转移预测优化              |     |

| 11.2 寄存器和指令的使用           |     |

| 11.3 避免重发自陷或冲突重试         | 112 |

| 11.4 数据流访问               |     |

| 11.5 低功耗优化               | 117 |

| 附录 A CSR 的限制             | 119 |

| <br>附录 В 事件计数内容与方法       |     |

| M录 C CHIP ID 定义          |     |

| ·····<br>附录 D 各种中断的初始向量值 |     |

| 附录 ε 修改记录                |     |

|                          |     |

# 1 核心结构概述

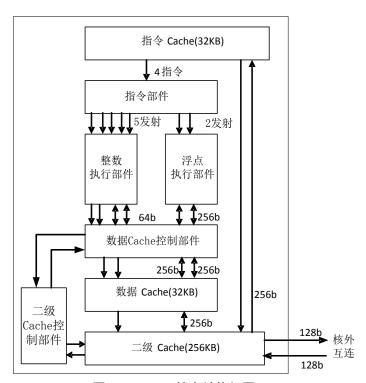

SW421 核心的基本结构如图 1-1 所示:

图 1-1 SW421 核心结构框图

SW421 由指令部件、整数执行部件、浮点执行部件、数据 Cache 控制部件、二级 Cache 控制部件以及一级指令 Cache、一级数据 Cache 和二级 Cache 组成。其技术特征如下:

- 1)继承申威 Core3 的指令系统,进行了少量的指令集扩展和修改;

- 2) 核心为采用并行发射、乱序发射、乱序执行和推测执行技术的4译码7发射超标量结构;

- 3) 采用短向量加速计算技术提高整数和浮点运算性能,支持浮点双 256 位 SIMD 流水线、整数单 256 位 SIMD 流水线,每个时钟周期可产生 11 个整数运算结果或 16 个浮点运算结果;

- 4) 一级指令 Cache 容量为 32KB, 采用四路组相联结构, 虚地址访问方式, Cache 行大小为 128 字节, 采用可容错的偶校验:

- 5) 一级数据 Cache 容量为 32KB,采用四路组相联结构,物理地址访问方式,Cache 行大小为 128 字节,采用可纠错的 ECC 校验:

- 6) 二级 Cache 容量为 512KB,采用八路组相联结构,物理地址访问方式,Cache 行大小为 128 字节,为指令和数据混合 Cache,采用可纠错的 ECC 校验;

- 7)一级数据 Cache 与二级 Cache 为严格的包含关系,一级指令 Cache 与二级 Cache 为既不包含,也不互斥关系,硬件自动支持指令与数据的 Cache 一致性。

# 2 处理器模式与特权程序

### 2.1 处理器模式

SW421 核心设置了 4 种处理器模式 (Processor Mode: PM), 具体定义如下:

- 1) 硬件模式 (Hardware Mode: HM): 最高级模式,为特权程序运行环境。此模式下,可使用特权指令直接对底层硬件进行控制和操作,可使用系统寄存器。指令流只能以物理地址访问,不进行虚实地址转换,数据流可以用物理地址访问,也可以用虚地址访问,由具体的访存指令决定。所有的中断被屏蔽,不响应任何中断请求;

- 2) 虚拟模式(Virtual Mode: VM): 次高级模式,介于硬件与操作系统之间,提供虚拟层服务。 此模式下,不能使用特权指令和系统寄存器,指令流和数据流可采用包括超页模式在内的 虚地址访问,由访问地址[52]位决定,允许响应中断请求;

- 3) 内核模式 (Kernel Mode: KM): 次低级模式,为操作系统运行环境。此模式下,不能使用特权指令和系统寄存器,指令流和数据流都采用虚地址访问(不支持超页模式),允许响应中断请求:

- 4) 用户模式(User Mode: UM): 最低级模式,为用户程序运行环境。此模式下,不能使用特权指令和系统寄存器,指令流和数据流都采用虚地址访问(不支持超页模式),允许响应中断请求。

程序计数器 PC 的最低两位用于记录当前处理器模式值,为" $00_2$ "表示硬件模式 (HM),为" $01_2$ "表示虚拟模式 (VM),为" $10_2$ "表示内核模式 (KM),为" $11_2$ "表示用户模式 (UM)。处理器模式有以下几种转换方式:

- 1) 非硬件模式下执行 SYS CALL 或者 SYS CALL/b 指令,可以从非硬件模式转换到硬件模式;

- 2) 核心响应中断请求时,可以从非硬件模式转换到硬件模式;

- 3) 核心发现异常时,可以从非硬件模式转换到硬件模式;

- 4) 硬件模式下执行 PRI\_RET 指令,可以从硬件模式转换到任意模式。

### 2.2 特权程序

特权程序是针对特定操作系统的一组程序,只能在 HM 模式下运行。在特权程序中,可使用五 条特权指令,读写处理器控制与状态寄存器,进行存储器管理等操作。

特权程序可以由以下事件触发:

- 1) 中断,包括复位、内部中断、外部中断和机器检查错等;

- 2) 异常,包括算术自陷和存储管理故障等;

- 3) SYS CALL或者 SYS CALL/b 指令。

特权程序主要应用于以下几种情况:

- 1) 一些必要的功能用硬件实现过于复杂,但又无法用常规程序来实现。如 TLB 装填、中断确 认和异常处理等:

- 一些必须为原子操作的功能,实现的指令序列较长,且需要访问底层硬件。如从异常或中 断返回等;

- 3) 一些为实现不同处理器之间的兼容或者减少编程工作量的功能,不经常使用,由专门硬件来实现的代价过大。

特权程序在指定的入口被调用,SW421 核心有两种特权程序入口,一种是 SYS\_CALL 和 SYS\_CALL/b 指令相关的特权程序入口,另一种是异常和中断相关的特权程序入口。

### 2.2.1 SYS\_CALL 和 SYS\_CALL/b 入口

SYS\_CALL 和 SYS\_CALL/b 指令的区别在于,前者不会中断指令流水线,而后者会中断指令流水线、并且在 ROB 空之后才会根据 SYS\_CALL/b 所指示的地址重新取指。两者用指令编码的[25]位加以区分:指令编码[25]位为"1"表示 SYS\_CALL,指令编码[25]位为"0"表示 SYS\_CALL/b。在 VM、KM 和 UM 模式下,执行 SYS\_CALL 或者 SYS\_CALL/b 指令时,会将指令流转到特权程序入口执行,入口地址由基址寄存器(PRI\_BASE)和指令功能码决定。SYS\_CALL 或者 SYS\_CALL/b 指令的返回地址由系统寄存器 SR23 来保存,其中 SR23[1:0]记录运行 SYS\_CALL 或者 SYS\_CALL/b 指令时的处理器模式。

SYS\_CALL 或者 SYS\_CALL/b 指令含一个入口程序地址相关的功能码,需要对该功能码的合法性进行检查,若其功能码满足以下任何一个条件,则产生非法操作码异常:

- 1) UM 模式下, SYS\_CALL 或者 SYS\_CALL/b 指令只能启动用户级特权程序,如果对应的指令功能码[7:0]位不在 0x80~0xBF(用户级特权程序)范围内,则产生非法操作码异常;

- 2) KM 模式下, SYS\_CALL 或者 SYS\_CALL/b 指令可以启动用户级和内核级特权程序,如果对应的指令功能码[7:0]位不在 0x00~0x3F(内核级特权程序)和 0x80~0xBF(用户级特权程序)范围内,则产生非法操作码异常;

- 3) VM 模式下, SYS\_CALL 或者 SYS\_CALL/b 指令可以启动用户级、内核级和虚拟级特权程序, 如果对应的指令功能码[7:0]位不在 0x00~0x3F(内核级特权程序)、0x80~0xBF(用户级特权程序)和 0x40~0x7F(虚拟级特权程序)范围内,则产生非法操作码异常;

- 4) UM、KM、VM 和 HM 模式下, SYS\_CALL 或者 SYS\_CALL/b 指令功能码[24:8]位不为全 "0",则产生非法操作码异常。

在 HM 模式下, SYS\_CALL 或者 SYS\_CALL/b 指令功能码[24:8]位为全 "0"则当作空指令。 SYS\_CALL 或者 SYS\_CALL/b 指令的功能码与其对应的特权程序入口地址(PC)的计算方法如下:

- 1) PC[63:48]=全"0";

- 2) PC[47:15]={PRI\_BASE[47:16], 0<sub>2</sub>};

- 3) PC[14:13]与功能码[7:6]的对应关系如表 2-1;

表 2-1SYS\_CALL 或者 SYS\_CALL/b 指令部分功能码与特权程序入口关系表

| 功能码[7:6] | PC[14:13] |

|----------|-----------|

| 102      | 112       |

| $00_{2}$ | $10_{2}$  |

| $01_{2}$ | 012       |

- 4) PC[12:7]=功能码[5:0];

- 5) PC[6:2]=全"0";

- 6) PC[1:0]= "00<sub>2</sub>" (进入 HM 模式的标志)。

由此可见,虚拟级特权程序起始偏移地址为 0x2000,内核级特权程序起始偏移地址为 0x4000,用户级特权程序起始偏移地址为 0x6000。2 条功能码相邻的 SYS\_CALL 或者 SYS\_CALL/b 指令的特权程序入口地址间距为 128 字节,即可以包含连续的 32 条指令,对于指令数量超过 32 条的特权程序,必须跳转到另一地址继续处理。

### 2.2.2 异常和中断入口

当硬件检测到没有屏蔽的异常或中断时,会自动跳到对应的特权程序入口进行处理。触发异常或被中断的指令 PC 值保存在异常地址寄存器(EXC\_PC)中。表 2-2 列出了各种异常入口相对于基址寄存器(PRI\_BASE)的偏移,表中各种异常或中断按优先级从低到高依次排列。

表 2-2 异常或中断服务特权程序入口偏移地址

| 序<br>号 | 入口名称          | 类型 | 偏移                                                     | 描述                                                                 |

|--------|---------------|----|--------------------------------------------------------|--------------------------------------------------------------------|

| 1      | DTBM_DOUBLE   | 故障 | 0x800 DTB 二次脱靶。指示 PRI_LDx/vpte 指令进行数据实地址转换时产生的 DTB 脱靶。 |                                                                    |

| 2      | DTBM_SINGLE_0 | 故障 | 0x880                                                  | DTB 用户脱靶。指示非 PRI_LDx/vpte 指令进行数据流虚实地址转换时产生的 DTB 脱靶且虚地址 VA[52]为"0"。 |

| 3      | DTBM_SINGLE_1 | 故障 | 0x900                                                  | DTB 核心脱靶。指示非 PRI_LDx/vpte 指令进行数据流虚实地址转换时产生的 DTB 脱靶且虚地址 VA[52]为     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |         | "1"。                        |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|-----------------------------|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 = 3:                  |         | ITB 用户脱靶。指示指令流进行虚实地址转换时产生   |

| 4   | ITB_MISS_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 故障                       | 0x980   | 的 ITB 脱靶且虚地址 VA[52]为 "0"。   |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.1 . tr <del>\$</del> r |         | ITB 核心脱靶。指示指令流进行虚实地址转换时产生   |

| 5   | ITB_MISS_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 故障                       | 0xA00   | 的 ITB 脱靶且虚地址 VA[52]为"1"。    |

|     | FEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | +47字                     | 0 400   | 浮点屏蔽故障。指示浮点屏蔽时运行浮点或 SIMD 扩  |

| 6   | FEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 故障                       | 0xA80   | 展指令产生的故障。                   |

| 7   | UNALIGN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 故障                       | 0xB00   | 不对界异常。指示数据流访问地址不对界产生的故障。    |

| 0   | ADITH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 算术                       | 0 D00   | 算术自陷。指示浮点或整数运算指令产生异常且对应     |

| 8   | ARITH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 自陷                       | 0xB80   | 的算术自陷使能。                    |

| 9   | 保留                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                        | 0xC00   |                             |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |         | 数据流故障。指示数据流地址越界、访问越权、数据     |

|     | DFAULT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 故障                       | 0xC80   | 流地址匹配、数据流数值匹配、数据流地址和数值同     |

| 10  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |         | 时匹配、虚地址符号检查错、数据 Cache 的标记偶校 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |         | 验错、数据 Cache 数据校验错、存储器数据多错等故 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |         | 障。                          |

| 11  | IA CV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 故障                       | 0. 500  | 指令流故障。指示指令流访问越权、虚地址符号检查     |

| 11  | IACV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 以悍                       | 0xD00   | 错、指令流地址匹配或目标地址匹配。           |

| 12  | OPCDEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 故障                       | 0xD80   | 操作码非法故障。指示出现非法的操作码或功能码。     |

| 13  | INTERRUPT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 中断                       | 0xE00   | 一般中断 0。指示产生了核间中断。           |

| 1.4 | DATE DATE OF THE STATE OF THE S | → N/C                    | 0. 1700 | 一般中断 1。指示产生了核间中断之外的普通硬件中    |

| 14  | INTERRUPT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 中断                       | 0xE80   | 断。                          |

| 15  | SLEEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 中断                       | 0xF00   | 睡眠中断。指示产生了请求核心进入睡眠状态的中断。    |

| 1.5 | MOTHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A Nort                   | 0. 1500 | 机器检查错中断。指示核心内部产生不能恢复的故障,    |

| 16  | МСНК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 中断                       | 0xF80   | 精确和不精确的机器检查错,都进入该入口。        |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | , <b>↓</b> , Nbr^        |         | 复位/睡眠唤醒中断。指示核心进入复位或从睡眠状态    |