| 参数 | 性能指标 |

| 核心数量 | 1 |

| 核心频率 | 典型工作频率: 800MHz~1.0GHz。 |

| 峰值运算速度 | 浮点: 每秒32亿次双精度浮点结果@800MHz; 整数: 每秒24亿次整数结果@800MHz。 |

| 工艺特征 | 40nm |

| 电压参数 | 申威111 LL: 内核电源: 0.95V±5%; 申威111 G: 内核电源: 1.1V±5%。 |

| Cache容量 | 核心包含两级Cache, Cache行长度为128字节; 一级Cache: 指令与数据分离, 容量分别为32KB, 均采用4路组相联结构; 二级Cache: 指令与数据混合, 容量为512KB, 采用8路组相联结构。 |

| 存储空间 | 支持64位虚地址空间, 实际实现43位虚地址; 支持40位物理地址。 |

| 存储器接口 | 16、 32或64位可配置的DDR3存储器接口, 可配置支持可配置的纠单错、 检双错 ECC校验, 最大传输率为1600MBps; 支持的总存储器容量为1GB、 2GB、 4GB或8GB; 支持连接DDR3 SDRAM芯片、 UDIMM和RDIMM存储器条。 |

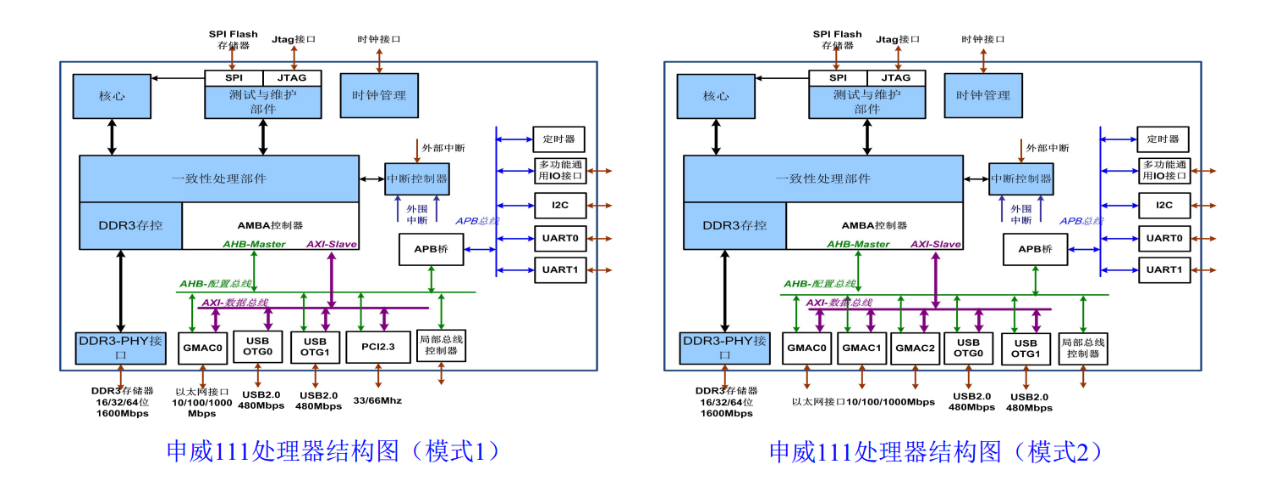

| I/O接口 | GMAC接口: 3路, 支持1000/100/10Mbps自适应以太网接口; USB 2.0接口: 2路, 符合USB-OTG 2.0协议, 支持Host和Device工作模式; PCI接口: 1路, 符合PCI 2.3接口协议, 支持66MHz、 33MHz总线频率; LBC接口: 异步局部总线扩展接口, 可外接Nor-Flash、 SRAM等IO设备; I2C接口: 符合I2C2.0接口协议, 最大传输率可达3.4MBps; UART接口: 符合16550编程模式的异步串行接口, 最大传输率可达115.2KBps, 支持数据字长、 停止位、 校验位可编程; 基于JTAG的维护与调试接口。 |

| 封装特性 | 采用BGA封装, 引脚数为744个; 芯片面积: 31mm×31 mm。 |

| 功耗 | 热设计功耗: 5W; 典型运行功耗: 3W@800MHz(含I/O功耗, 与具体应用相关) 。 |